The Hidden AI Bottleneck: Why CoWoS Packaging Supply Chain is the Real Constraint

Everyone looks at silicon yield, but the real bottleneck for AI chips is hidden in the packaging layer. Discover why CoWoS materials—sourced 90% from Japan—are becoming the industry's critical choke point, and why packaging verification is now a strategic battleground.

Everyone is obsessed with AI chips—NVIDIA H100s, Blackwells, customs silicon from hyperscalers. But the real constraint holding back the AI revolution isn't the silicon die itself. It's the packaging.

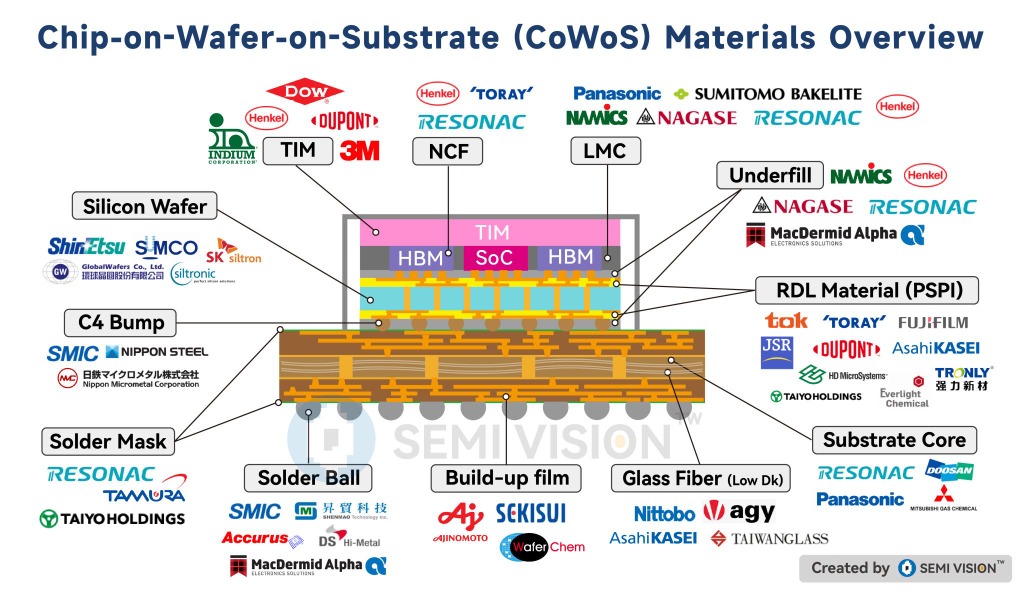

Chip-on-Wafer-on-Substrate (CoWoS) has quietly become one of the most critical choke points in the entire semiconductor stack. It's not just about stacking dies; it's about securing a complex, fragile ecosystem of advanced materials that makes that stacking possible. For teams in hardware validation and packaging verification, this supply chain fragility introduces massive new risks.

Anatomy of a Bottlebeck

A CoWoS package isn't just "glued" together. It relies on a precise symphony of advanced materials, each with its own supply chain constraints:

Redistribution Layers (RDL)

Critical for signal routing; relies on high-purity photosensitive polyimides (PSPI).

Underfill & TIMs

Thermal Interface Materials and underfills prevent the chip from cooking itself or cracking under stress.

Advanced Substrates

The ABF (Ajinomoto Build-up Film) substrate shortage of 2021 is a warning of what can happen here.

Solder Balls & Bumps

Microbumps connecting dies are shrinking to microns, demanding atomic-level purity.

The 90% Factor: Japanese Dominance

Here’s the part most people underestimate: More than 90% of backend materials used in CoWoS come from Japanese suppliers.

Companies like Resonac, Ajinomoto, Shin-Etsu, and JSR hold near-monopolies on key chemical formulations. This dominance worked when volumes were steady. But with AI driving aggressive CoWoS ramps, these specialized suppliers are struggling to scale production fast enough.

The Validation Scramble: Qualifying Second Sources

When a primary material runs short, OSATs (Outsourced Semiconductor Assembly and Test) providers race to qualify second sources. This is a nightmare for packaging validation.

Re-Qualification Hell

Changing a single underfill material requires months of reliability testing—thermal cycling, stress testing, and electromigration validation to ensure the new material doesn't cause field failures.

Material Interactions

A new TIM might react differently with the heat spreader or the silicon die. Hardware validation teams must verify that chemical interactions won't lead to delamination over time.

Advanced Packaging is the New Battleground

The shift is subtle, but unmistakable: Advanced packaging is no longer just a supporting function of the semiconductor industry. It is becoming the competitive battleground. CoWoS isn't just about stacking dies; it's about securing the entire materials ecosystem behind them.

We still talk about nodes and silicon, but leverage is quietly moving downstream. The companies that can secure their supply of ABF substrates, specialized underfills, and high-purity solder are the ones who will actually ship chips in 2026.